Memtest Failure Analysis

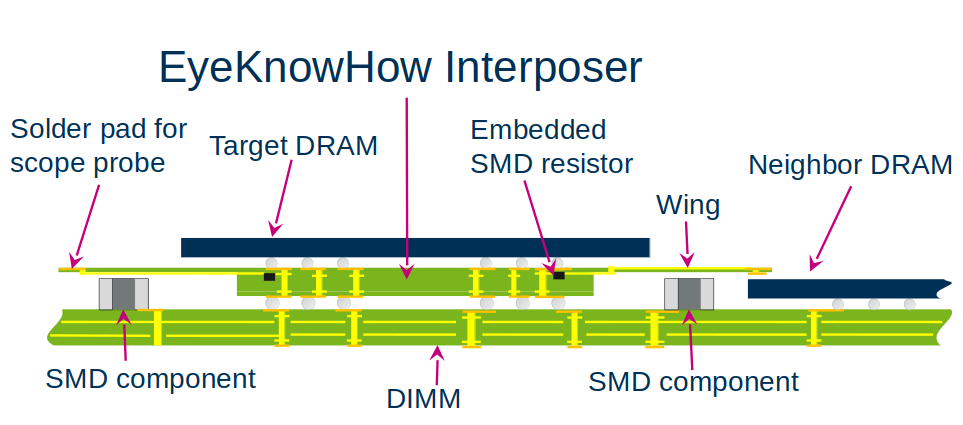

What finally needs to be done on any new design with a memory interface is often forgotten. While there is a comprehensive measurement procedure defined for e. g. PCI-Express, there is only the DRAM spec available for the memory interface. Nevertheless, it is absolutely required to measure the margins of the design to figure out if it is stable enough for High Volume Manufacturing (HVM). Beside compliance tests there are two “simple” tests available to quantify signal margin:

- VREF margin test by adjusting VREF

- Timing margin test by changing phase relation between critical timing signals

VREF margin tests are simple to implement: Just overwrite the nominal reference voltage and run a memory test. The timing margin tests would be even simpler… if the corresponding controller register settings are known. When combining these two tests, it is even possible to generate a data eye for the signal that the receiver really sees!

But most important is the evaluation of memory test log files. Understanding the output of a memory test is essential to analyse the problem of a design. From the log file one can learn:

- Was the error related to the CA or DQ interface?

- Was it during Read or Write?

- Was it a DQS or a single DQ problem?

- Is it related to a specific memory row or column address and therefore device related?

This kind of information is absolutely required to do meaningful fail analysis. Evaluating log files during a signal margin test identifies most critical issues and countermeasures can be defined.

Image Gallery

EyeKnowHow

Hermann Ruckerbauer

Itzlinger Straße 21a

94469 Deggendorf

Germany

Phone: +49 991 29692905

Fax: +49 991 98158793

Mobile: +49 176 78778777

Hermann.Ruckerbauer@EyeKnowHow.de