Cost Reduction

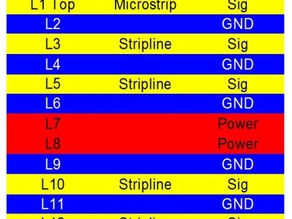

Today everything is related to cost. In terms of cost, your design needs to compete with cheapest designs from Far East, certainly at a higher performance level. This is only possible if the design space is evaluated carefully. One example is the stack-up. Below are four different stack-ups with 6 routing layers. The first is a perfect implementation for a high-speed design. No X-talk between layers and also the intralayer X-talk (between two signals on one layer) is very limited. However, is it necessary to have such an expensive 14 layer stack-up?

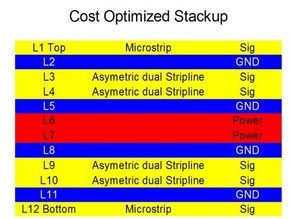

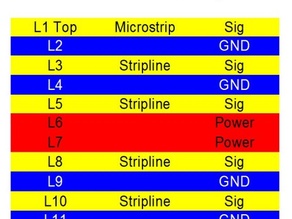

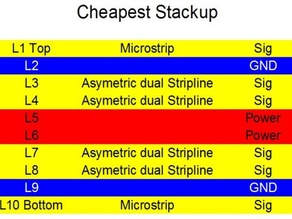

The second picture shows an example where there are still 6 routing layers, but implemented only on 12 layers. X-talk is slightly worse due to the asymmetric double stripline routing. However, for most applications this will still work fine. Considering especially a memory interface there are some special things to keep in mind: The midlevel thevenin termination and the power reverenced CA bus on commodity systems. The midlevel thevenin termination will gain from a ground AND power referencing for driving “0” or “1”. Additionally, DRAMs are designed for a power referenced CA bus. So why not utilizing this feature? An example is shown in the third picture: This alternative stack-up would allow the CA routing on L5 and L8 , still having the advantage of a perfectly implemented stripline. And finally, both ideas could be combined as shown in the last picture. Here the CA is completely power-referenced, being state of the art for commodity systems. And: we are down to a 10 layer board still having 6 routing layers. This stack-up might be only suitable for some special applications, but it is way better than you may think!

For such a design simulations should be performed to get to know the impact of stack-up on signal integrity. Additional efforts needs to be spent to ensure the power routing for other parts of the board. Overall split planes are better than many people think. If a split plane is implemented correctly, it behaves as good as an ideal full plane. So it is a question of cost: reducing the layer count by 4 layers versus the additional design effort for a correct implementation! However this is mainly valid for the first design. Once you know how to deal with this implementation the following designs will not require higher design effort as “conventional” designs!

Image Gallery

EyeKnowHow

Hermann Ruckerbauer

Itzlinger Straße 21a

94469 Deggendorf

Germany

Phone: +49 991 29692905

Fax: +49 991 98158793

Mobile: +49 176 78778777

Hermann.Ruckerbauer@EyeKnowHow.de